Транзисторна еволюция: От планарни до CFET, 3D интеграцията предефинира прогреса на полупроводниците

Повече от половин век полупроводниковата индустрия се развиваше, като следваше едно просто правило: направете транзисторите по-малки.Намаляването на размерите на функциите осигурява по-висока производителност, по-ниска мощност и по-ниска цена на транзистор.Но днес този път е достигнал своя физически и икономически предел.Ерата на чистото мащабиране приключи и идва нова ера структурна иновация и 3D интеграция е започнало.

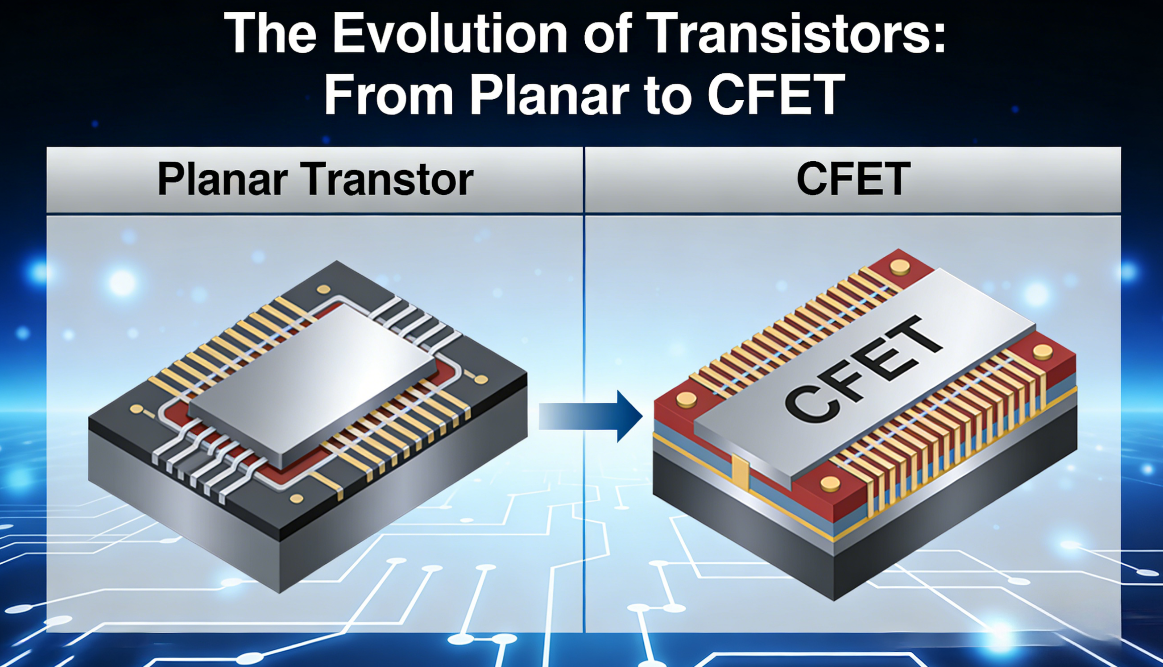

Самият транзистор претърпява пълна архитектурна революция.От равнинен MOSFET до FinFET, от GAA нанолист до CFET подреждане, всяка стъпка представлява преминаване от свиване към възстановяване на транзистора в три измерения.Това не е просто постепенно подобрение – това е пълно предефиниране на начина, по който чиповете осигуряват производителност.

Четирите поколения транзисторна архитектура

1. Планарен транзистор (традиционен 2D)

Класическата плоска структура, където портата контролира канала отгоре.Той доминираше от първите дни до 40nm и 28nm.Тъй като размерите се свиха допълнително, токът на утечка и електростатичният контрол се превърнаха в неразрешими проблеми.

2. FinFET (3D Gate Control)

Каналът се превръща във вертикална „перка“, като портата се увива около три страни.Това драстично подобрява електростатичния контрол, намалява изтичането и позволява намаляване на мащаба до 7nm, 5nm и дори 3nm.FinFET стана основата на съвременната ера на високопроизводителни чипове.

3. GAA Nanosheet (Gate-All-Around)

При 2n и по-ниски, FinFET достига своя лимит.GAA заменя перката с подредени хоризонтални нанопроводници или листове, изцяло заобиколени от портата.Осигурява по-добър контрол, по-ниска мощност и по-висок задвижващ ток.GAA вече е основната структура за чипове от клас 2nm в TSMC, Samsung и Intel.

4. CFET (допълнителен FET)

Следващата граница: подреждане на NMOS и PMOS вертикално.CFET събира два транзистора в отпечатъка на един, драстично намалява площта и подобрява плътността.Това е крайният еволюционен край на транзисторното мащабиране, преди истинската 3D системна интеграция да поеме надмощие.

Защо мащабирането само по себе си вече не работи

- Разходите за процес нарастват експоненциално при всеки нов възел

- Квантовото изтичане и физическите ограничения втвърдяват ограниченията

- Забавянето на свързването и консумацията на енергия изпреварват скоростта на транзистора

- Големите монолитни чипове страдат от нисък добив и висока цена

Индустрията осъзна: производителността вече не идва от по-малки транзистори.Идва от по-добри връзки, по-интелигентна архитектура и вертикална интеграция.

Новата ера: Три нива на 3D иновация

Напредъкът на полупроводниците сега се определя от три измерения на 3D дизайна:

- 3D транзистор: FinFET, GAA, CFET – изграждане на транзистора вертикално

- 3D подреждане на устройства: Логическа памет, хибридно свързване, подреждане на SRAM

- 3D системна интеграция: Chiplet, 2.5D/3D опаковка, интеграция, базирана на interposer

Заедно те образуват 3D×3D×3D ера: транзисторът, устройството и системата стават триизмерни.

DTCO: Новата основна компетентност

Когато мащабирането приключи, Съвместно оптимизиране на технологията на проектиране (DTCO) става критично.Това означава съвместно проектиране на архитектура, транзисторна структура, метално насочване и опаковка от самото начало.Най-силните компании вече не са просто лидери на процеси – те са интегратори на системно ниво.

Ефективността на окабеляването, захранването, топлинният дизайн и плътността на честотната лента сега определят реалната производителност на продукта.

AI е най-добрата движеща сила

AI и високопроизводителните изчисления изискват безпрецедентна честотна лента, енергийна ефективност и плътност.Тези изисквания не могат да бъдат изпълнени чрез традиционно мащабиране.Те изискват:

- Взаимосвързаност памет-компютър със свръхвисока честотна лента

- Изключителна енергийна ефективност на операция

- Масивен паралелизъм и плътна интеграция

AI принуди цялата индустрия да се откаже от чистото мащабиране и да прегърне пълната 3D хетерогенна интеграция.

Заключение: Бъдещето не е по-малко, то е по-високо

Ерата на свиващите се транзистори избледнява.Бъдещето на полупроводниците не е в това да правим устройствата по-малки - то е в изграждането на системи по-високи, по-плътни и по-интелигентно свързани.

От Planar до FinFET до GAA до CFET, транзисторът завърши своята еволюция.Следващата битка ще се води 3D интеграция, усъвършенствано опаковане и дизайн на системно ниво.Това е мястото, където ще се реши следващото десетилетие на лидерство в полупроводниците.